## SH366302R5/006R5Y-BAA00

## CONTENTS

- [1] General Description

- [2] Block Diagram

- [3] Pin Descriptions

- [4] Absolute Maximum Ratings

- [5] Electrical Characteristics

- [6] Function Description

- [7] Test Circuits

- [8] Typical Application Schematic

- [9] Timing Chart

- [10] Package Dimensions

- [11] Carrier Tape and Reel Information

- [12] Mark Specification

- [13] Product Name Structure

- [14] Modification record

#### 1 General Description

SH366302 is a protection IC for lithium-ion/lithium polymer rechargeable batteries, including voltage detection circuits with strict accuracy and delay circuits. It aims for protecting 1-cell lithium-ion/lithium polymer rechargeable battery packs from overcharged, overdischarged, and over-current status.

The SH366302 is a high voltage tolerance CMOS-based protection IC for rechargeable one-cell lithium-ion/ lithium polymer battery, aiming to detect over-charged/over-discharged status of one-cell Li+, along with excessive load current and charge current, protect the battery from the conditions described above. What's more, SH366302 contains short-circuit protector function to prevent excessive short-circuit current.

When the SH366302 detects over-charged voltage or charging over-current, the output of CHG pin switches to "L"(low) level after the internally fixed delay time. When the SH366302 detects over-discharged voltage or discharging over-current, the output of DSG pin switches to "L"(low) level after the internally fixed delay time.

After detecting over-charged voltage, the output of CHG can returns "H"(high) when one of the two following requirements is met:

(1)the cell voltage decreases lower than  $V_{\text{OVR}}$  (over-charged release voltage);

(2)the cell voltage decreases lower than  $V_{OV}$  (over-charged detection voltage),and a discharging current is detected (the load is connected to the circuit).

After detecting over-discharged voltage, the output of DSG pin returns to "H" when one of the two following requirements is met.

(1)The cell voltage increases higher than  $V_{UVR}$  (over-discharged release voltage);

(2) the cell voltage gets higher than  $V_{UV}$  (over-discharged detection voltage),and a charger is connected.

When the charging over-current is detected, SH366302 will quit the charging over-current status and CHG returns to "H" level if the load circuit is connected.

When the discharging over-current or short-circuit current is detected, SH366302 will quit the discharging over-current or short-circuit status and DSG pin returns to "H" level if the load circuit is removed.

| Part.No                 | V <sub>ov</sub> | V <sub>ovr</sub> | V <sub>UV</sub> | V <sub>UVR</sub> | V <sub>DOC1</sub> | V <sub>DOC2</sub> | V <sub>SC</sub> | V <sub>SC2</sub> | V <sub>coc</sub> |

|-------------------------|-----------------|------------------|-----------------|------------------|-------------------|-------------------|-----------------|------------------|------------------|

|                         | (V)             | (V)              | (V)             | (V)              | (mV)              | (mV)              | (mV)            | (YES/NO)         | (mV)             |

| SH366302R5/006R5Y-BAA00 | 4.530           | 4.380            | 2.100           | 2.300            | 10.5              | 15.0              | 40              | YES              | -18              |

续上表:

| Part.No                 | t <sub>ov</sub><br>(s) | t <sub>∪∨</sub><br>(ms) | t <sub>DOC1</sub><br>(S) | t <sub>DOC2</sub><br>(ms) | t <sub>sc</sub><br>(µs) | t <sub>coc</sub><br>(ms) | 0V Battery Charge<br>(Allowed/<br>Forbidden) | Power Down<br>Mode<br><b>(YES/NO)</b> |

|-------------------------|------------------------|-------------------------|--------------------------|---------------------------|-------------------------|--------------------------|----------------------------------------------|---------------------------------------|

| SH366302R5/006R5Y-BAA00 | 1.0                    | 64                      | 3.584                    | 16                        | 280                     | 16                       | Allowed                                      | YES                                   |

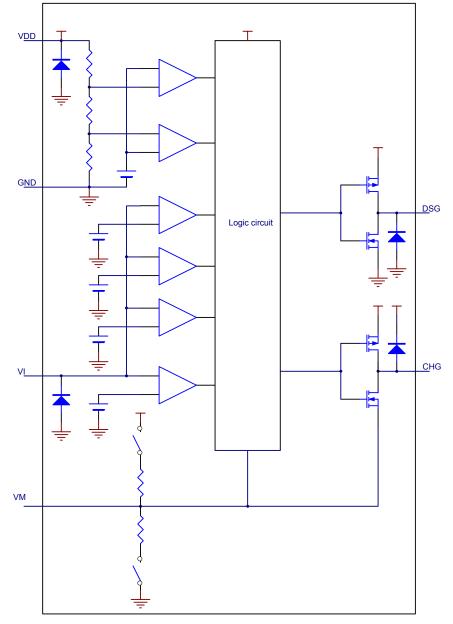

## 2 Block Diagram

Fig 1. SH366302 Block Diagram

#### 3 Pin Configuration

| VM  | 1 |          | 6 VI  |

|-----|---|----------|-------|

| CHG | 2 | SH366302 | 5 VDD |

| DSG | 3 |          | 4 GND |

### Fig 2. Pin Configuration of SH366302

#### Table1. SH366302 pin description

| Pin NO. | Pin Name | I/O | Function Description                 |

|---------|----------|-----|--------------------------------------|

| 1       | VM       | I   | Load and charger detection pin;      |

| 2       | CHG      | 0   | Drive pin of charge MOSFET;          |

| 3       | DSG      | 0   | Drive pin of discharge MOSFET;       |

| 4       | GND      | Р   | Input pin for negative power supply; |

| 5       | VDD      | Р   | Input pin for positive power supply; |

| 6       | VI       | I   | Current detection pin;               |

Total 6 pins.

#### 4 Absolute maximum ratings

|                                           |          | (Ta                             | a=25°C,GND=0V) |

|-------------------------------------------|----------|---------------------------------|----------------|

| Item                                      | Pin Name | Absolute Maximum Ratings        | Unit           |

| VM pin input voltage                      | VM       | VDD-28 to VDD+0.3               | V              |

| CHG pin output voltage                    | CHG      | V <sub>VM</sub> -0.3 to VDD+0.3 | V              |

| DSG pin output voltage                    | DSG      | GND-0.3 to VDD+0.3              | V              |

| Input voltage between VDD pin and GND pin | VDD      | GND-0.3 to GND+6.0              | V              |

| VI pin input voltage                      | VI       | GND-0.3 to VDD+0.3              | V              |

| Operation ambient temperature             | -        | -40 to 85                       | °C             |

| Storage temperature                       | -        | -40 to 125                      | °C             |

*Note1:* If the actual operating parameter exceeds the range of absolute maximum ratings, the components of SH366302 will be permanently damaged. Only when the operating parameters are among the regulated range above, the relevant functions can be guaranteed in normal working status.

#### 5 Electrical characteristics

### 5.1 Electrical characteristics(unless otherwise specified, Ta=25°C)

| Symbol            | Item                                         | Min.     | Тур.     | Max.     | Unit | Test<br>Circuit |

|-------------------|----------------------------------------------|----------|----------|----------|------|-----------------|

| V <sub>OV</sub>   | Overcharge detection voltage                 | 4.510    | 4.530    | 4.550    | V    | А               |

| $V_{\text{OVR}}$  | Overcharge release voltage                   | 4.330    | 4.380    | 4.430    | V    | А               |

| t <sub>ov</sub>   | Overcharge detection delay time              | 0.7      | 1.0      | 1.3      | s    | В               |

| t <sub>ovr</sub>  | Overcharge release delay time                | 0.65     | 1.0      | 1.5      | ms   | В               |

| t <sub>ovhr</sub> | Overcharge hysteresis release delay time     | 150      | 250      | 500      | μs   | В               |

| $V_{\text{UV}}$   | Overdischarge detection voltage              | 2.050    | 2.100    | 2.150    | V    | А               |

| $V_{\text{UVR}}$  | Overdischarge release voltage                | 2.225    | 2.300    | 2.375    | V    | А               |

| t <sub>UV</sub>   | Overdischarge detection delay time           | 44.8     | 64.0     | 83.2     | ms   | В               |

| t <sub>UVR</sub>  | Overdischarge release delay time             | 0.7      | 5.0      | 11.7     | ms   | В               |

| t <sub>UVHR</sub> | Overdischarge hysteresis release delay time  | 0.65     | 1.0      | 1.5      | ms   | В               |

| t <sub>PD</sub>   | delay time of entering Power Down Mode       | 0.4      | 1.0      | 2.5      | ms   | В               |

| t <sub>PDR</sub>  | delay time of quitting Power Down Mode       | 0.7      | 1.0      | 1.3      | ms   | В               |

| V <sub>DOC1</sub> | Discharge overcurrent 1 detection voltage    | 9.0      | 10.5     | 12.0     | mV   | В               |

| t <sub>DOC1</sub> | Discharge overcurrent 1 detection delay time | 2.509    | 3.584    | 4.659    | S    | В               |

| V <sub>DOC2</sub> | Discharge overcurrent 2 detection voltage    | 12       | 15       | 18       | mV   | В               |

| t <sub>DOC2</sub> | Discharge overcurrent 2 detection delay time | 11.2     | 16.0     | 20.8     | ms   | В               |

| $V_{SC}$          | Short circuit detection voltage              | 36       | 40       | 44       | mV   | В               |

| t <sub>sc</sub>   | Short circuit detection delay time           | 196      | 280      | 364      | μs   | В               |

| $V_{SC2}$         | Short circuit 2 detection voltage            | VDD-1.4  | VDD-0.8  | VDD-0.3  | V    | В               |

| V <sub>DOCR</sub> | Discharge overcurrent release voltage        | 0.78*VDD | 0.83*VDD | 0.86*VDD | V    | В               |

| t <sub>DOCR</sub> | Discharge overcurrent release delay time     | 0.65     | 1.0      | 1.5      | ms   | В               |

| V <sub>coc</sub>  | Charge overcurrent detection voltage         | -19.5    | -18.0    | -16.5    | mV   | В               |

| t <sub>coc</sub>  | Charge overcurrent detection delay time      | 11.2     | 16.0     | 20.8     | ms   | В               |

| t <sub>COCR</sub> | Charge overcurrent release delay time        | 160      | 250      | 375      | μs   | В               |

| Symbol            | Item                                                                                    | Min.     | Тур.     | Max.     | Unit | Test<br>Circuit |

|-------------------|-----------------------------------------------------------------------------------------|----------|----------|----------|------|-----------------|

| $V_{CHGH}$        | CHG output high voltage                                                                 | VDD-0.15 | VDD-0.02 | VDD      | V    | F               |

| $V_{\text{DSGH}}$ | DSG output high voltage                                                                 | VDD-0.15 | VDD-0.02 | VDD      | V    | F               |

| $V_{LD}$          | Load detection voltage                                                                  | 0.3      | 0.35     | 0.4      | V    | В               |

| $V_{CD1}$         | Charger detection voltage                                                               | GND-0.01 | GND      | GND+0.01 | V    | В               |

| $V_{CD2}$         | Charger detection voltage 2                                                             | 0.6      | 0.7      | 1.2      | V    | В               |

| $V_{0CHA}$        | Minimum charger voltage                                                                 | 0.7      | 1.1      | 1.5      | V    | D               |

| I <sub>cc</sub>   | Current consumption (normal status)                                                     | 1        | 2        | 3        | μA   | С               |

| I <sub>PD</sub>   | Current consumption of sleep status                                                     | 0.01     | 0.03     | 0.05     | μA   | С               |

| R <sub>DH</sub>   | Internal pull-up resistance of DSG pin                                                  | 0.5      | 1.0      | 1.7      | kΩ   | D               |

| R <sub>CH</sub>   | Internal pull-up resistance of CHG pin                                                  | 1.2      | 2.5      | 5.0      | kΩ   | D               |

| $R_{DL}$          | Internal pull-down resistance of DSG pin                                                | 2.1      | 3.1      | 4.1      | kΩ   | D               |

| $R_{CL}$          | Internal pull-down resistance of CHG pin                                                | 1.6      | 2.5      | 4.0      | kΩ   | D               |

| t <sub>DH</sub>   | The time during the period that the DSG pin rises from GND to VDD-0.5                   | 3        | 8        | 15       | μs   | E               |

| t <sub>DL</sub>   | The time during the period that the DSG pin decreases from VDD-0.5 to GND               | 10       | 35       | 100      | μs   | E               |

| t <sub>CH</sub>   | The time during the period that the CHG pin rises from the voltage of VM to VDD-0.5     | 10       | 25       | 40       | μs   | Е               |

| t <sub>CL</sub>   | The time during the period that the CHG pin decreases from VDD-0.5 to the voltage of VM |          | 47       | 60       | μs   | E               |

| $R_{VMS}$         | Internal pull-down resistance of VM pin                                                 | 7.5      | 10       | 15       | kΩ   | С               |

| $R_{VMD}$         | Internal pull-up resistance of VM pin                                                   | 0.5      | 1.25     | 2.5      | MΩ   | С               |

| Symbol            | Item                                         | Min.     | Тур.     | Max.     | Unit | Test<br>Circuit |

|-------------------|----------------------------------------------|----------|----------|----------|------|-----------------|

| V <sub>OV</sub>   | Overcharge detection voltage                 | 4.505    | 4.530    | 4.555    | V    | А               |

| V <sub>OVR</sub>  | Overcharge release voltage                   | 4.325    | 4.380    | 4.435    | V    | А               |

| t <sub>ov</sub>   | Overcharge detection delay time              | 0.6      | 1.0      | 1.4      | s    | В               |

| t <sub>ovr</sub>  | Overcharge release delay time                | 0.5      | 1.0      | 2.0      | ms   | В               |

| t <sub>ovhr</sub> | Overcharge hysteresis release delay time     | 125      | 250      | 500      | μs   | В               |

| $V_{\text{UV}}$   | Overdischarge detection voltage              | 2.045    | 2.100    | 2.155    | V    | А               |

| $V_{\text{UVR}}$  | Overdischarge release voltage                | 2.215    | 2.300    | 2.385    | V    | А               |

| t <sub>UV</sub>   | Overdischarge detection delay time           | 38.4     | 64.0     | 89.6     | ms   | В               |

| t <sub>UVR</sub>  | Overdischarge release delay time             | 0.6      | 5.0      | 12.6     | ms   | В               |

| t <sub>UVHR</sub> | Overdischarge hysteresis release delay time  | 0.5      | 1.0      | 2.0      | ms   | В               |

| t <sub>PD</sub>   | delay time of entering Power Down Mode       | 0.4      | 1.0      | 2.5      | ms   | В               |

| t <sub>PDR</sub>  | delay time of quitting Power Down Mode       | 0.6      | 1.0      | 1.4      | ms   | В               |

| $V_{\text{DOC1}}$ | Discharge overcurrent 1 detection voltage    | 8.5      | 10.5     | 12.5     | mV   | В               |

| t <sub>DOC1</sub> | Discharge overcurrent 1 detection delay time | 2.330    | 3.584    | 4.838    | S    | В               |

| $V_{\text{DOC2}}$ | Discharge overcurrent 2 detection voltage    | 12.0     | 15.0     | 18.0     | mV   | В               |

| t <sub>DOC2</sub> | Discharge overcurrent 2 detection delay time | 9.6      | 16.0     | 22.4     | ms   | В               |

| $V_{\text{SC}}$   | Short circuit detection voltage              | 35.4     | 40.0     | 44.5     | mV   | В               |

| t <sub>sc</sub>   | Short circuit detection delay time           | 168      | 280      | 392      | μs   | В               |

| $V_{SC2}$         | Short circuit 2 detection voltage            | VDD-1.4  | VDD-0.8  | VDD-0.3  | V    | В               |

| V <sub>DOCR</sub> | Discharge overcurrent release voltage        | 0.78*VDD | 0.83*VDD | 0.86*VDD | V    | В               |

| t <sub>DOCR</sub> | Discharge overcurrent release delay time     | 0.5      | 1.0      | 2.0      | ms   | В               |

| V <sub>COC</sub>  | Charge overcurrent detection voltage         | -20.0    | -18.0    | -16.0    | mV   | В               |

| t <sub>coc</sub>  | Charge overcurrent detection delay time      | 9.6      | 16.0     | 22.4     | ms   | В               |

| t <sub>COCR</sub> | Charge overcurrent release delay time        | 125      | 250      | 500      | μs   | В               |

## 5.2 Electrical characteristics(unless otherwise specified, Ta=-25°C~70°C)

| Symbol            | Item                                                                                    | Min.     | Тур.     | Max.     | Unit | Test<br>Circuit |

|-------------------|-----------------------------------------------------------------------------------------|----------|----------|----------|------|-----------------|

| V <sub>CHGH</sub> | CHG output high voltage                                                                 | VDD-0.15 | VDD-0.02 | VDD      | V    | F               |

| $V_{\text{DSGH}}$ | DSG output high voltage                                                                 | VDD-0.15 | VDD-0.02 | VDD      | V    | F               |

| $V_{LD}$          | Load detection voltage                                                                  | 0.3      | 0.35     | 0.4      | V    | В               |

| V <sub>CD1</sub>  | Charger detection voltage                                                               | GND-0.01 | GND      | GND+0.01 | V    | В               |

| V <sub>CD2</sub>  | Charger detection voltage 2                                                             | 0.6      | 0.7      | 1.2      | V    | В               |

| V <sub>0CHA</sub> | Minimum charger voltage                                                                 | 0.5      | 1.1      | 1.7      | V    | D               |

| I <sub>cc</sub>   | Current consumption (normal status)                                                     | 1        | 2        | 4        | μA   | С               |

| I <sub>PD</sub>   | Current consumption of sleep status                                                     | 0.01     | 0.03     | 0.1      | μA   | С               |

| R <sub>DH</sub>   | Internal pull-up resistance of DSG pin                                                  | 0.5      | 1.0      | 1.7      | kΩ   | D               |

| R <sub>CH</sub>   | Internal pull-up resistance of CHG pin                                                  | 1.2      | 2.5      | 5.0      | kΩ   | D               |

| $R_{DL}$          | Internal pull-down resistance of DSG pin                                                | 2.1      | 3.1      | 4.1      | kΩ   | D               |

| R <sub>CL</sub>   | Internal pull-down resistance of CHG pin                                                | 1.6      | 2.5      | 4.0      | kΩ   | D               |

| t <sub>DH</sub>   | The time during the period that the DSG pin rises from GND to VDD-0.5                   | 3        | 8        | 15       | μs   | E               |

| t <sub>DL</sub>   | The time during the period that the DSG pin decreases from VDD-0.5 to GND               | 10       | 35       | 100      | μs   | E               |

| t <sub>CH</sub>   | The time during the period that the CHG pin rises from the voltage of VM to VDD-0.5     | 10       | 25       | 40       | μs   | Е               |

| t <sub>CL</sub>   | The time during the period that the CHG pin decreases from VDD-0.5 to the voltage of VM |          | 47       | 60       | μs   | E               |

| R <sub>VMS</sub>  | Internal pull-down resistance of VM pin                                                 | 7.5      | 10       | 15       | kΩ   | С               |

| $R_{VMD}$         | Internal pull-up resistance of VM pin                                                   | 0.25     | 1.25     | 3.5      | MΩ   | С               |

| Symbol            | Item                                         | Min.     | Тур.     | Max.     | Unit | Test<br>Circuit |

|-------------------|----------------------------------------------|----------|----------|----------|------|-----------------|

| V <sub>OV</sub>   | Overcharge detection voltage                 | 4.495    | 4.530    | 4.565    | V    | А               |

| $V_{\text{OVR}}$  | Overcharge release voltage                   | 4.320    | 4.380    | 4.440    | V    | А               |

| t <sub>ov</sub>   | Overcharge detection delay time              | 0.5      | 1.0      | 1.5      | s    | В               |

| t <sub>ovr</sub>  | Overcharge release delay time                | 0.5      | 1.0      | 2.0      | ms   | В               |

| t <sub>ovhr</sub> | Overcharge hysteresis release delay time     | 125      | 250      | 500      | μs   | В               |

| $V_{\text{UV}}$   | Overdischarge detection voltage              | 2.040    | 2.100    | 2.160    | V    | А               |

| $V_{\text{UVR}}$  | Overdischarge release voltage                | 2.200    | 2.300    | 2.400    | V    | А               |

| t <sub>UV</sub>   | Overdischarge detection delay time           | 32.0     | 64.0     | 96.0     | ms   | В               |

| t <sub>UVR</sub>  | Overdischarge release delay time             | 0.5      | 5.0      | 13.5     | ms   | В               |

| t <sub>UVHR</sub> | Overdischarge hysteresis release delay time  | 0.5      | 1.0      | 2.0      | ms   | В               |

| t <sub>PD</sub>   | delay time of entering Power Down Mode       | 0.4      | 1.0      | 2.5      | ms   | В               |

| t <sub>PDR</sub>  | delay time of quitting Power Down Mode       | 0.5      | 1.0      | 1.5      | ms   | В               |

| $V_{\text{DOC1}}$ | Discharge overcurrent 1 detection voltage    | 8.5      | 10.5     | 12.5     | mV   | В               |

| t <sub>DOC1</sub> | Discharge overcurrent 1 detection delay time | 1.792    | 3.584    | 5.376    | s    | В               |

| $V_{\text{DOC2}}$ | Discharge overcurrent 2 detection voltage    | 11.5     | 15.0     | 18.5     | mV   | В               |

| t <sub>DOC2</sub> | Discharge overcurrent 2 detection delay time | 8        | 16       | 24       | ms   | В               |

| $V_{\text{SC}}$   | Short circuit detection voltage              | 35.5     | 40.0     | 44.5     | mV   | В               |

| t <sub>sc</sub>   | Short circuit detection delay time           | 140      | 280      | 420      | μs   | В               |

| $V_{SC2}$         | Short circuit 2 detection voltage            | VDD-1.4  | VDD-0.8  | VDD-0.3  | V    | В               |

| V <sub>DOCR</sub> | Discharge overcurrent release voltage        | 0.78*VDD | 0.83*VDD | 0.86*VDD | V    | В               |

| t <sub>DOCR</sub> | Discharge overcurrent release delay time     | 0.5      | 1.0      | 2.0      | ms   | В               |

| V <sub>COC</sub>  | Charge overcurrent detection voltage         | -20.0    | -18.0    | -16.0    | mV   | В               |

| t <sub>coc</sub>  | Charge overcurrent detection delay time      | 8.0      | 16.0     | 24.0     | ms   | В               |

| t <sub>COCR</sub> | Charge overcurrent release delay time        | 125      | 250      | 500      | μs   | В               |

### 5.3 Electrical characteristics(unless otherwise specified, Ta=-40°C~85°C)

| Symbol            | Item                                                                                    | Min.     | Тур.     | Max.     | Unit | Test<br>Circuit |

|-------------------|-----------------------------------------------------------------------------------------|----------|----------|----------|------|-----------------|

| $V_{\text{CHGH}}$ | CHG output high voltage                                                                 | VDD-0.15 | VDD-0.02 | VDD      | V    | F               |

| $V_{\text{DSGH}}$ | DSG output high voltage                                                                 | VDD-0.15 | VDD-0.02 | VDD      | V    | F               |

| $V_{LD}$          | Load detection voltage                                                                  | 0.3      | 0.35     | 0.4      | V    | В               |

| V <sub>CD1</sub>  | Charger detection voltage                                                               | GND-0.01 | GND      | GND+0.01 | V    | В               |

| V <sub>CD2</sub>  | Charger detection voltage 2                                                             | 0.6      | 0.7      | 1.2      | V    | В               |

| V <sub>0CHA</sub> | Minimum charger voltage                                                                 | 0.5      | 1.1      | 1.7      | V    | D               |

| I <sub>cc</sub>   | Current consumption (normal status)                                                     | 1        | 2        | 4        | μA   | С               |

| I <sub>PD</sub>   | Current consumption of sleep status                                                     | 0.01     | 0.03     | 0.1      | μA   | С               |

| R <sub>DH</sub>   | Internal pull-up resistance of DSG pin                                                  | 0.5      | 1.0      | 1.7      | kΩ   | D               |

| $R_{CH}$          | Internal pull-up resistance of CHG pin                                                  | 1.2      | 2.5      | 5.0      | kΩ   | D               |

| $R_{DL}$          | Internal pull-down resistance of DSG pin                                                | 2.1      | 3.1      | 4.1      | kΩ   | D               |

| R <sub>CL</sub>   | Internal pull-down resistance of CHG pin                                                | 1.6      | 2.5      | 4.0      | kΩ   | D               |

| t <sub>DH</sub>   | The time during the period that the DSG pin rises from GND to VDD-0.5                   | 3        | 8        | 15       | μs   | E               |

| t <sub>DL</sub>   | The time during the period that the DSG pin decreases from VDD-0.5 to GND               | 10       | 35       | 100      | μs   | Е               |

| t <sub>CH</sub>   | The time during the period that the CHG pin rises from the voltage of VM to VDD-0.5     | 10       | 25       | 40       | μs   | Е               |

| t <sub>CL</sub>   | The time during the period that the CHG pin decreases from VDD-0.5 to the voltage of VM |          | 47       | 60       | μs   | E               |

| R <sub>VMS</sub>  | Internal pull-down resistance of VM pin                                                 | 7.5      | 10       | 15       | kΩ   | С               |

| $R_{VMD}$         | Internal pull-up resistance of VM pin                                                   | 0.25     | 1.25     | 3.5      | MΩ   | С               |

*Note2:* The current flowing into the chip is negative, such as leak current. The current flowing out of the chip is positive, such as power consumption, pull current.

Note3: Refer to test circuits in chapter 7.

#### 6 Function Description

#### 6.1 Normal status

When all the following conditions are satisfied, SH366302 is in normal status:

(1). The battery voltage is between  $V_{UV}$  (over-discharged detection voltage) and  $V_{OV}$  (over-charged detection voltage);

(2). The VI pin voltage of SH366302 is between  $V_{COC}$  (charging over-current detection voltage) and  $V_{DOC1}$  (discharging over-current 1 detection voltage);

(3). CHG pin outputs VDD, DSG pin outputs VDD, charge and discharge MOSFET are both turned on.

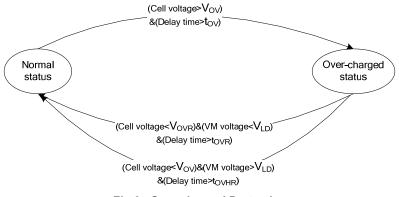

#### 6.2 Over-charged status

When all the following conditions are satisfied, SH366302 enters over-charged status and turns off the charge MOSFET:

(1). The battery voltage is higher than  $V_{\text{OV}}$  (over-charged detection voltage);

(2). The condition of (1) lasts up to t<sub>OV</sub> (over-charged detection delay time) or longer;

When one of the following conditions is satisfied, the over-charged status is released, and the charge MOSFET is turned on:

(1). The voltage of the VM pin is lower than  $V_{LD}$  (without load connection), and the cell voltage is lower than  $V_{OVR}$  (over-charged release voltage), lasting up to  $t_{OVR}$  (over-charged release delay time) or longer;

(2). The voltage of the VM pin is higher than  $V_{LD}$  (with load connection), lasting up to  $t_{OVHR}$  (over-charged release hysteresis delay time) or longer, and the cell voltage is lower than  $V_{OV}$  (over-charged detection voltage);

# *Note1:* When SH366302 is in over-charged status, the discharging over-current detection and short-circuit detection function is disabled.

Fig 3. Over-charged Protection

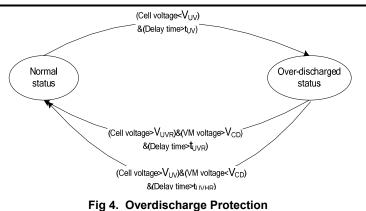

#### 6.3 Over-discharged status

When all the following conditions are satisfied, SH366302 enters over-discharged status and turns off the discharge MOSFET, the internal pull-up resistance is also turned on:

(1). The cell voltage is lower than  $V_{UV}$ (over-discharged detection voltage);

(2). The condition (1) lasts up to  $t_{UV}$  (over-discharged detection delay time) or longer;

When one of the following conditions is satisfied, the over-discharged status is released, and the discharge MOSFET is turned on:

(1). The voltage of the VM pin is not lower than  $V_{CD1}$  (without charger plugged in), and the cell voltage is higher than  $V_{UVR}$ , lasting up to  $t_{UVR}$  (delay time of over-discharged release detection);

(2). The voltage of the VM pin is lower than  $V_{CD1}$  (with charger plugged in),lasting up to tUVHR (delay time of over-discharged release hysteresis) or longer, and the cell voltage is higher than VUV(over-discharged detection voltage);

#### Note2: When cell voltage is lower than V<sub>UV</sub>, the charging overcurrent detection function is disabled.

#### 6.4 Power Down satus

When the system is over-discharged,SH366302 will enter Power Downstatus when all the following conditions are satisfied,and the internal pull-up resistance of SH366302 is turned on:

(1). The voltage of VM pin is higher than VDD-0.8;

(2). The condition of (1) lasts for longer than  $t_{\text{PD}}$  (delay time of entering Power Down Status ).

When system is in Power DownStatus,SH366302 will quit the Power Downstatus when all the following conditions are satisfied,and the system enters into over-discharged status.

(1). The voltage of VM pin is lower than V<sub>CD2</sub>(typical value of charger detection voltage2);

(2). The condition of (1) lasts for longer than  $t_{PDR}$  (delay time of quitting Power Down Status).

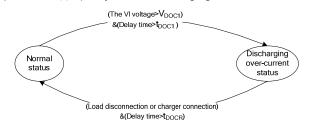

#### 6.5 Discharging over-current status

SH366302 has three levels for discharging over-current protection,  $V_{DOC1}$  (discharging over-current 1 detection voltage) is lower than  $V_{DOC2}$  (discharging over-current 1 detection voltage),  $V_{DOC2}$  is lower than  $V_{SC}$ (short-circuit detection voltage),  $t_{DOC1}$ (delay time of discharging over-current detection 1) is larger than  $t_{DOC2}$ (delay time of discharging over-current detection 2),  $t_{DOC2}$ is larger than  $t_{SC}$  (short-circuit detection delay time).

When all the following conditions are satisfied, SH366302 enters discharging over-current status and turns off the discharge MOSFET:

(1). The VI pin voltage of SH366302 is higher than  $V_{DOC1}/V_{DOC2}/V_{SC}$ ;

(2). The condition of (1) lasts up to  $t_{DOC1}/t_{DOC2}/t_{SC}$  or longer;

When all the following conditions are satisfied, the discharging over-current status is released:

- (1). Load is disconnected or charger is connected(the VM voltage is lower than V<sub>DOCR</sub>);

- (2). The condition of (1) lasts up to the t<sub>DOCR</sub> (delay time of discharging over-current release)or longer.

Fig 5. Discharging over-current 1 Protection

Note3: When SH366302 is in discharging over-current status, SH366302 will turn on the internal pull-down resistance and pull VM pin down to GND, in order to judge whether the outside load is removed.

#### 6.6 Discharging short-circuit 2 status

SH366302 contains discharging short-circuit 2 protection, when both of the following conditions are satisfied, system enters discharging short-circuit 2 status and turns off the discharge MOSFET:

- (1). The VM pin voltage is higher than V<sub>SC2</sub>(discharging short-circuit 2 detection voltage);

- (2). The condition (1) lasts up to  $t_{SC}$ ;

When all the following conditions are satisfied, the discharging short-circuit 2 status is released:

- (1). The load is disconnected or the charger is connected (the voltage of VM pin is lower than  $V_{DOCR}$ );

- (2). The condition (1) lasts up to  $t_{\text{DOCR}}$ ;

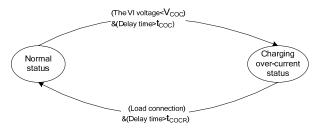

#### 6.7 Charging over-current status

SH366302 contains charging over-current protection function, when all the following conditions are satisfied, system enters charging over-current status and turns off the charge MOSFET:

(1). The VI pin voltage of SH366302 is lower than V<sub>COC</sub>(charging over-current detection voltage);

(2). The condition of (1) lasts longer than  $t_{COC}$  (delay time of charging over-current detection);

When all the following conditions are satisfied, the charging over-current status is released:

- (1). The load is connected (the voltage of the VM pin is higher than  $V_{LD}$ );

- (2). The condition of (1) lasts longer than t<sub>COCR</sub>(delay time of charging over-current release);

Fig 6. Charging over-current Protection

#### 6.8 Function for 0V battery charging

When the battery voltage is 0V, the battery can be charged if using a charger the voltage of which is higher than  $V_{0CHA}$ , actual required voltage of the charger varies according to different threshold voltage of charge MOSFET.

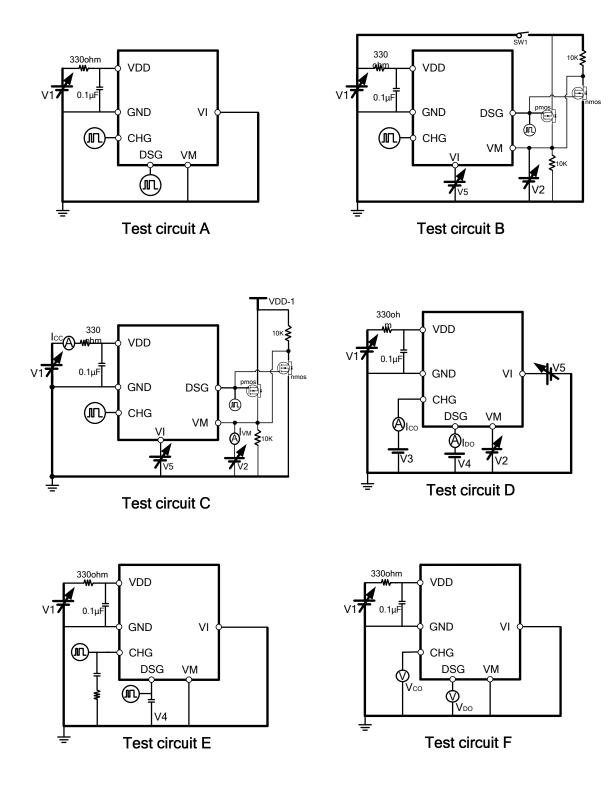

#### 7 Test Circuits

7-1. Overcharge detection voltage ( $V_{OV}$ ) & Overcharge release voltage( $V_{OVR}$ )

【Test Circuit】: A

[Description]: Set V1=3.4V, connect VM and VI to GND. Increase V1 until the voltage of CHG pin drop to low, the present V1 is  $V_{OV}$ . Then decrease V1 from present voltage, until the voltage of CHG pin returns to normal, similarly, is  $V_{OVR}$ .

7-2. Overdischarge detection voltage (V $_{\rm UV}$ ) & Overdischarge release voltage (V $_{\rm UVR})$

【Test Circuit】: A

[Description]: Set V1=3.4V,connect VM and VI to GND.Decrease V1 until the voltage of DSG pin drop to low, the present V1 is  $V_{UV}$ . Then Increase V1 from present voltage,until DSG pin returns to normal,similarly, is  $V_{UVR}$ .

7-3. Discharge overcurrent 1 detection voltage (V<sub>DOC1</sub>)

【Test Circuit】: B

[Description]: Set V1=3.4V,V5=0V, disconnect VM from V2,connect switch1.Increase V5 until the following two requirements are satisfied.Then,the present V5 is V<sub>DOC1</sub>.

(1)The DSG pin shuts down;

(2)The delay time between the rise of V5 and shutting down of DSG is aroud 3.584s.

7-4. Discharge overcurrent 2 detection voltage (V<sub>DOC2</sub>)

【Test Circuit】: B

[Description]: Set V1=3.4V,V5=0V,disconnect VM from V2,connect switch1.Increase V5 until the following two requirements are satisfied.Then,the present V5 is  $V_{DOC2}$ .

(1)The DSG pin shuts down;

(2)The delay time between the rise of V5 and shutting down of DSG is aroud 16ms.

7-5. Short circuit detection voltage( $V_{SC}$ )

【Test Circuit】: B

[Description]: Set V1=3.4V,V5=0V,disconnect VM from V2,connect switch1.Increase V5 until the following two requirements are satisfied.Then,the present V5 is  $V_{SC}$ .

(1)The DSG pin shuts down;

(2)The delay time between the rise of V5 and shutting down of DSG is aroud 280 $\mu s.$

7-6. Short circuit detection voltage(V<sub>SC2</sub>)/ Discharge overcurrent release voltage (V<sub>DOCR</sub>)

【Test Circuit】: C

[Description]: Set V1= VDD-1=3.4V,V2=V5=0V.Increase V2 until DSG pin shuts down, the present V2 is  $V_{SC2}$ . Then decrease V2 to 0V, decrease VDD-1 of the extra test circuit until DSG pin returns high, similarly, is  $V_{DOCR}$ .

7-7. Charge overcurrent detection voltage (V<sub>COC</sub>)

【Test Circuit】: B

[Description]: Set V1=3.4V,V2=V5=0V,disconnect switch1.Decrease V5 until CHG pin shuts down.Then,the present V5 is  $V_{COC}$ .

000

7-8. Load detection voltage (V<sub>LD</sub>)

【Test Circuit】: B

[Description]: Set V1=4.7V,V2=V5=0V,disconnect switch1,the CHG pin turns low,then decrease V1 to 4.45V.Increase V2 till the point where CHG returns high. The present V2 is  $V_{LD}$ .

7-9. Charger detection voltage (V<sub>CD1</sub>)

【Test Circuit】: B

[Description]: Set V1=2.0V,V5=0V,V2=0.1V,disconnect switch1,the DSG pin turns low. Then increase V1=2.2V. Decrease V2 gradually, if V2 is decreased to 0V while DSG still keeps low, then continue decrease V2 to negative( adjustment step is 1mV), till the DSG returns high. The present V2 is the V<sub>CD1</sub>.

7-10. Charger detection voltage 2(V<sub>CD2</sub>)

[Test Circuit]: B

[Description]: Set V1=2.0V,V5=0V,V2=1.0V,disconnect switch1,the DSG pin turns low. Then increase V1=2.7V. Decrease V2 gradually till the DSG returns high. The present V2 is the  $V_{CD2}$ .

7-11. Operating current in normal mode(I<sub>CC</sub>)

【Test Circuit】: C

[Description]: Set V1=3.4V,V5=V2=0V.Record the current at IC's VDD pin.

7-12. Current consumption of over-discharged status ( $I_{\text{PD}}$ )

【Test Circuit】: C

[Description]: Set V1=V2=1.8V,V5=0V.DSG pin turns down.Record the current at IC's VDD pin,which is IPD.

7-13. Internal pull-down resistance of VM pin ( $R_{VMS}$ ) [Test Circuit]: C

[Description]: Set VDD=3.4V,V5=18mV, disconnect VM from V2,DSG pin turns low.Record the current at IC's VM pin  $I_{VM}$ , then calculate the result:  $R_{VMS}$ =3.4V/  $I_{VM}$ .

- 7-14. Internal pull-up resistance of VM pin ( $R_{VMD}$ ) [Test Circuit]: C [Description]: Set V1=2.0V, V2=V5=0V.Record the current at IC's VM pin  $I_{VM}$ ,and calculate the  $R_{VMD}$ =V1/ $I_{VM}$ .

- 7-15. Internal pull-up resistance of DSG pin  $(R_{DH})$

- Test Circuit ]: D

[Description]: Set V1=4.0V, V2=V5=0V, V3=V4=3.5V, obtain the current flowing out the DSG pin I<sub>D0</sub>.R<sub>DH</sub>=0.5V/ I<sub>D0</sub>.

7-16. Internal pull-up resistance of CHG pin (R<sub>CH</sub>)

7-17. Internal pull-down resistance of DSG pin (R<sub>DL</sub>)

【Test Circuit】: D

[Description]: Set VDD=2.2V,V2=V5=0V,V4=0.1V,system enter over-discharge protection system and DSG pin turns down.Obtain the current sinking into the DSG pin  $I_{CO.}R_{DL}$ =0.5V/  $I_{CO.}$

7-18. Internal pull-down resistance of CHG pin (R<sub>CL</sub>)

【Test Circuit】: D

[Description]: Set VDD=4.7V,V2=V5=0V,V3=0.1V, system enter over-charge protection system and CHG pin turns down.Obtain the current sinking into the CHG pin  $I_{CO}$ . R<sub>DL</sub>=0.5V/  $I_{CO}$ .

7-19. Overcharge detection delay time  $(t_{OV})$

【Test Circuit】: B

[Description]: Set V1=3.4V,V2=V5=0V,disconnect switch1,system operates in normal status. Then change V1 swiftly to 4.7V,the delay time between the point where V1 is higher than the actual  $V_{OV}$  and shutting down of CHG is exactly the  $t_{OV}$ .

7-20. Overdischarge detection delay time  $(t_{\text{UV}})$

【Test Circuit】: B

[Description]: Set V1=3.4V,V2=V5=0V,disconnect switch1,system operates in normal status. Then change V1 swiftly to 2.0V,the delay time between the point where V1 is lower than the actual  $V_{UV}$  and shutting down of DSG is exactly the  $t_{UV}$ .

7-21. Discharge overcurrent 1 detection delay time  $(t_{\text{DOC1}})$

【Test Circuit】: B

[Description]: Set V1=3.4V, disconnect VM from V2, connect switch1. Set V5=12mV, connect VI to V5 swiftly, the delay time between the rise of VI and shutting down of DSG is exactly the  $t_{DOC1}$ .

7-22. Discharge overcurrent 2 detection delay time  $(t_{\text{DOC2}})$

【Test Circuit】: B

[Description]: Set V1=3.4V, disconnect VM from V2, connect switch1.Set V5=18mV, connect VI to V5 swiftly, the delay time between the rise of VI and shutting down of DSG is exactly the  $t_{DOC2}$ .

7-23. Short circuit detection voltage (t<sub>SC</sub>)

【Test Circuit】: B

[Description]: Set V1=3.4V, disconnect VM from V2, connect switch1.Set V5=44mV, connect VI to V5 swiftly, the delay time between the rise of VI and shutting down of DSG is exactly the  $t_{SC}$ .

7-24. Charge overcurrent detection delay time (t<sub>COC</sub>)

【Test Circuit】: B

[Description]: Set V1=3.4V,V2=0V,disconnect switch1.Set V5=-19.5mV,connect VI to V5 swiftly,the delay time between the drop of VI and shutting down of CHG is exactly the  $t_{COC}$ .

7-25. Minimum charger voltage ( $V_{0CHA}$ )

【Test Circuit】: D

[Description]: Set V1=V5=0V,V2=V3=-0.5V.Decrease V2 till the point where the current at IC's CHG pin is higher than  $1.0\mu$ A.Then,the V<sub>0CHA</sub>=-V2.

#### Note4: When testing 7-3(V<sub>DOC1</sub>),7-4(V<sub>DOC2</sub>),7-5(V<sub>SC</sub>),7-6(V<sub>SC2</sub>&V<sub>DOCR</sub>),7-12(R<sub>VMS</sub>),7-20(t<sub>DOC1</sub>),7-21(t<sub>DOC2</sub>),7-22(t<sub>SC</sub>), the VDD-1 will be adjusted only in 7-6, so we should add another 3.4V to VDD-1, in the other items, the VDD-1 can be connected to V1 directly for convenience.

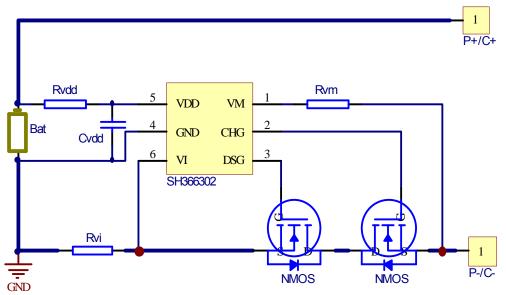

8 Typical application schematic

### 8.1 Application schematic of SH366302

#### Fig 8. Application schematic of SH366302

8.2 External Components

|   | Symbol           | Min.  | Тур. | Max. | Unit |

|---|------------------|-------|------|------|------|

| 1 | R <sub>vdd</sub> | 100   | 330  | 1000 | Ω    |

| 2 | $C_{vdd}$        | 0.068 | 0.1  | 1    | μF   |

| 3 | R <sub>vm</sub>  | 100   | 470  | 1000 | Ω    |

| 4 | R <sub>vi</sub>  | 1     | 3    | 20   | mΩ   |

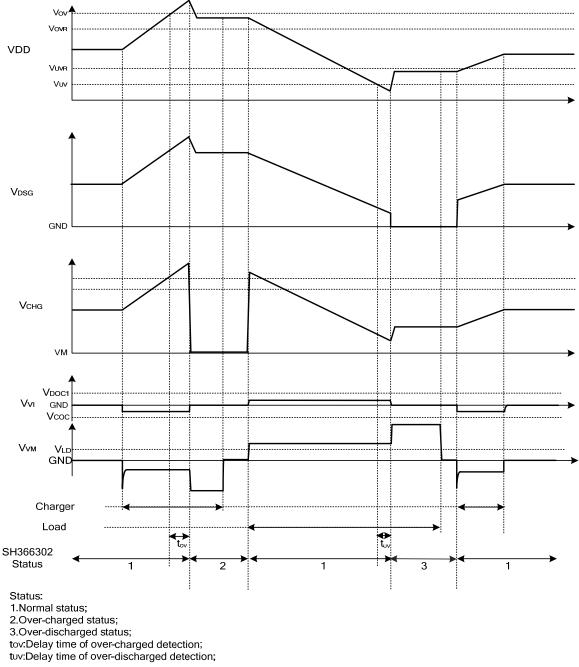

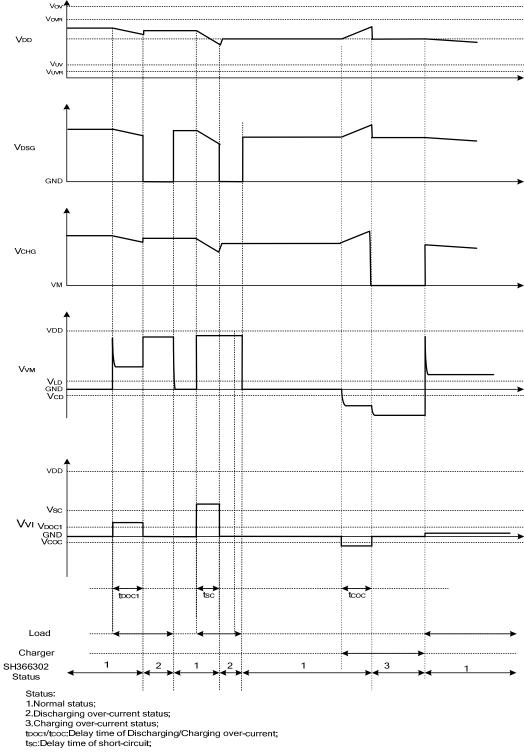

#### 9 **Timing Chart**

## 9.1 Over-voltage and Under-voltage Operation

#### 9.2 Over-current Operation

unit: mm

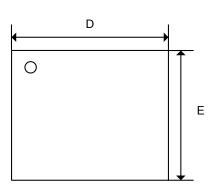

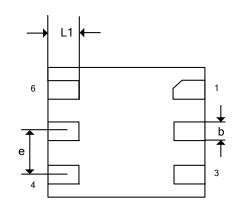

### 10 Package dimensions

DFN 6L (1.57 X 1.9) (P0.50 T 0.55) Outline Dimensions

Top View

**Bottom View**

Side View

| Symbol | Dimensions in mm |       |      |  |

|--------|------------------|-------|------|--|

|        | MIN              | NOR   | MAX  |  |

| A      | 0.5              | 0.55  | 0.6  |  |

| A2     | 0                | 0.025 | 0.05 |  |

| D      | 1.8              | 1.9   | 2.0  |  |

| E      | 1.47             | 1.57  | 1.67 |  |

| b      | 0.17             | 0.22  | 0.27 |  |

| е      | 0.5TYP           |       |      |  |

| L1     | 0.25             | 0.30  | 0.35 |  |

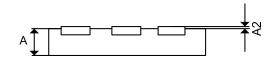

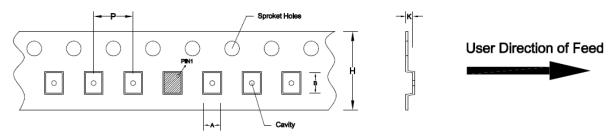

## 11 Carrier Tape and Reel Infromation

DFN6L (1.57\*1.9)

unit: mm

# **Carrier Tape Dimensions**

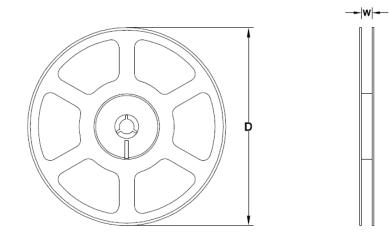

# **Reel Dimensions**

### \*All dimensions are nominal

| А | 1.71 | Dimension designed to accommodate the component width     |  |

|---|------|-----------------------------------------------------------|--|

| В | 2.08 | Dimension designed to accommodate the component length    |  |

| К | 0.71 | Dimension designed to accommodate the component thickness |  |

| Н | 8    | Overall width of the carrier tape                         |  |

| Р | 4    | Pitch between successive cavity centers                   |  |

| W | 8.4  | Reel width                                                |  |

| D | 178  | Reel diameter                                             |  |

#### 12 Mark Specification

(1)~④: Product abbreviations (5BAA);

(5)~⑧: Lot Number;

Last row: Year & month

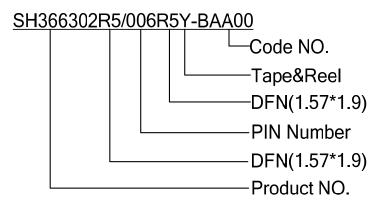

13 Product Name Structure

#### 14 Modification record

| Modification record of SH366302 (BAA)                                                                                                                                                             |               |            |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|--|--|

| Detailed description                                                                                                                                                                              | Located pages | Date       |  |  |

| Original version V0.0                                                                                                                                                                             | -             | 2019/12/25 |  |  |

| Remove the parameter $I_{UV}$ in the sheet                                                                                                                                                        | P6/8/10       | 2020/07/16 |  |  |

| Add the specific description about test circuit                                                                                                                                                   | P11/12/13     | 2020/07/16 |  |  |

| Change the upper and lower limit of $R_{VMS}$ in the sheet                                                                                                                                        | P6/8/10       | 2020/09/14 |  |  |

| Add the description about discharging short-circuit 2 $V_{SC2}$                                                                                                                                   | P5/7/9/13/14  | 2020/09/14 |  |  |

| Revise the test description and test circuit diagram                                                                                                                                              | P14/15/16/17  | 2020/10/21 |  |  |

| Change the test condition when measuring current consumption in<br>over-discharged status                                                                                                         | P15           | 2020/11/04 |  |  |

| Add the typical,Max and Min value in the sheet                                                                                                                                                    | P5~P10        | 2020/11/20 |  |  |

| Revise the package dimensions                                                                                                                                                                     | P21           | 2020/12/09 |  |  |

| Convert the parameters which reflect drive capability from $I_{DH}$ , $I_{CH}$ , $I_{DL}$ , $I_{CL}$ to $R_{DH}$ , $R_{CH}$ , $R_{DL}$ , $R_{CL}$ ,meanwhile,revise the related test description. | P6/8/10,P15   | 2020/12/23 |  |  |

| Convert $R_{DL}$ in the sheet from 0.5k $\Omega$ to 3.1k $\Omega$ @Typical                                                                                                                        | P6/8/10       | 2021/01/25 |  |  |

|                                                                                                                                                                                                   |               |            |  |  |